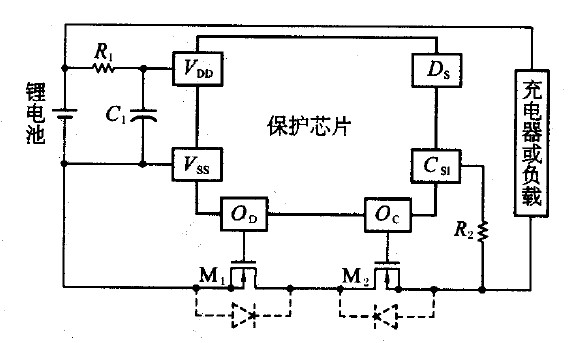

图1中,R1可以增强VDD脚的ESD能力,并同C1一起可减小VDD的波动。R2则在电池发生过放电后接入充电器或充电器接反的情况下能够避免闩锁效应。在保护回路的设计上,由于芯片内置延时产生电路,故应用时DS端悬空就省去了一个电容,而且电池板体积可以进一步缩小,这样便降低了系统成本。

图1设计的保护回路主要由两个MOSFET和专用保护IC构成。专用保护IC即本文设计的电路,负责监视电池电压、放电电流、并控制两个MOSFET的栅极,而MOSFET分别实现充电和放电的控制功能。图1中,VDD为过充电和过放电的检测端,也是正电源输入端;VSS为保护电路的接地点;OC为充电控制端;OD为放电控制端;CSI为过流检测端;DS端用于减小延时相关指标的测试时间,应用时悬空即可。